# PX4 飞行控制器参考设计

PX4 参考设计是 Pixhawk 系列 的飞行控制器。该设计于 2011 年首次发布,现已进入第 5 个年头。 一代 (第六代电路板设计正在进行中)。

# 二进制兼容性

根据特定设计生产的所有电路板都应具有二进制兼容性(即可以运行相同的固件)。从 2018 年起,我们将提供二进制兼容性测试套件,以验证和认证这种兼容性。

第 1-3 代 FMU 是作为开放硬件设计的,而第 4 和第 5 代 FMU 仅提供引脚和电源规格(原理图由各个制造商创建)。为了更好地确保兼容性,FMUv6 及以后的版本将重新采用完整的参考设计模型。

# 参考设计世代

- FMUv1:开发板(STM32F407、128 KB RAM、1 MB 闪存、 图式 (打开新窗口))(PX4 不再支持)

- FMUv2:Pixhawk(STM32F427,168 MHz,192 KB RAM,1 MB 闪存、 图式 (打开新窗口))

- FMUv3:带 2MB 闪存的 Pixhawk 变体(3DR Pixhawk 2 (Solo)、Hex Pixhawk 2.1、Holybro Pixfalcon、3DR Pixhawk Mini、STM32F427、168 MHz、256 KB RAM、2 MB 闪存、 图式 (打开新窗口))

- FMUv4:Pixracer(STM32F427,168 MHz,256 KB RAM,2 MB 闪存、 引脚 (打开新窗口))

- FMUv4 PRO:Drotek Pixhawk 3 PRO(STM32F469,180 MHz,384 KB RAM,2 MB 闪存、 引脚 (打开新窗口))

- FMUv5:Holybro Pixhawk 4(STM32F765,216 MHz,512 KB RAM,2 MB 闪存、 引脚 (打开新窗口))

- FMUv6:正在开发中,最终名称待定,变体 6s(STM32H7,400 MHz,2 MB RAM,2 MB 闪存)和变体 6i(i.MX RT1050,600 MHz,512 KB RAM,外部闪存)。

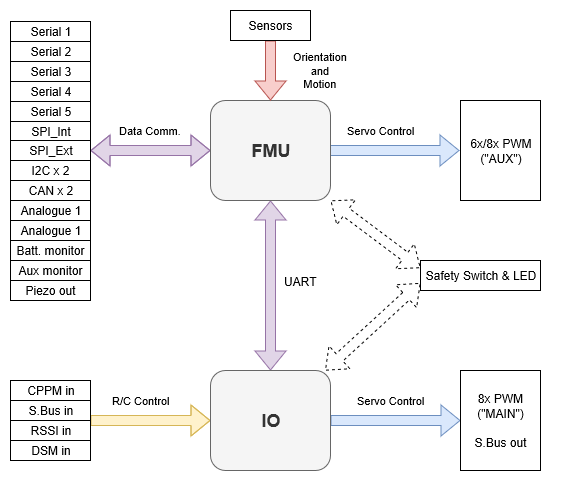

# 主/IO 功能分解

下图显示了 Pixhawk 系列飞行控制器中 FMU 和 I/O 板之间的总线和功能责任划分(这些板集成在一个物理模块中)。

有些 Pixhawk 系列控制器不带 I/O 板,以减少空间或降低复杂性,或更好地满足某些板的使用要求。在这种情况下 SYS_USE_IO 设置为 0 这样就不会启动 I/O 驱动程序。还可以设置 SYS_USE_IO 至 0 来禁用飞行控制器上存在但不需要的 I/O(以略微减轻 CPU 负载)。

备注

制造商生产的不带 I/O 板的飞行控制器变体通常被命名为包含 I/O 板的变体的缩写:例如,"quot;diminutive"。 Pixhawk 4 迷你型_, CUAV v5 纳米.

必须在带有 I/O 板的飞行控制器上运行的构建目标将 FMU 输出映射到 辅助 和 I/0 输出到 MAIN (见上图)。如果目标机在没有 I/O 板或 I/O 板被禁用的硬件上运行,则不会出现 PWM MAIN 输出。例如,运行 px4_fmu-v5_default 关于 Pixhawk 4 (带 IO)和 Pixhawk 4 Mini (无输入/输出)。

警告

关于 Pixhawk 4 Mini 这就造成了 MAIN 飞行控制器上的丝网印刷标签和 辅助 在 执行机构配置.

请注意,如果构建目标只打算在没有 I/0 板的飞行控制器上运行,那么 FMU 输出将被映射到 MAIN 例如 px4_fmu-v4_default 目标为 Pixracer).

PX4 PWM 输出被映射到以下任一接口 MAIN 或 辅助 港口 执行机构配置.

← 硬件仿真 制造商电路板支持指南 →